# A Real-Time-capable Hard- and Software Architecture for Joint Image and Knowledge Processing in Cognitive Automobiles

Matthias Goebl and Georg Färber {goebl,faerber}@rcs.ei.tum.de

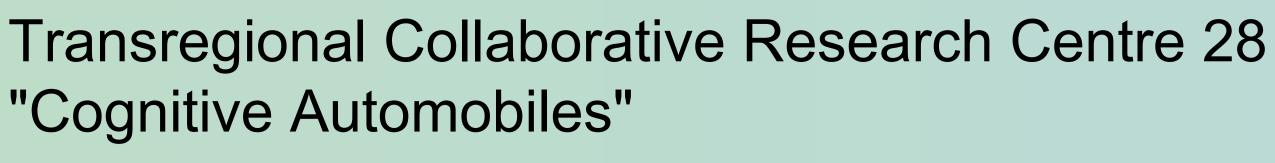

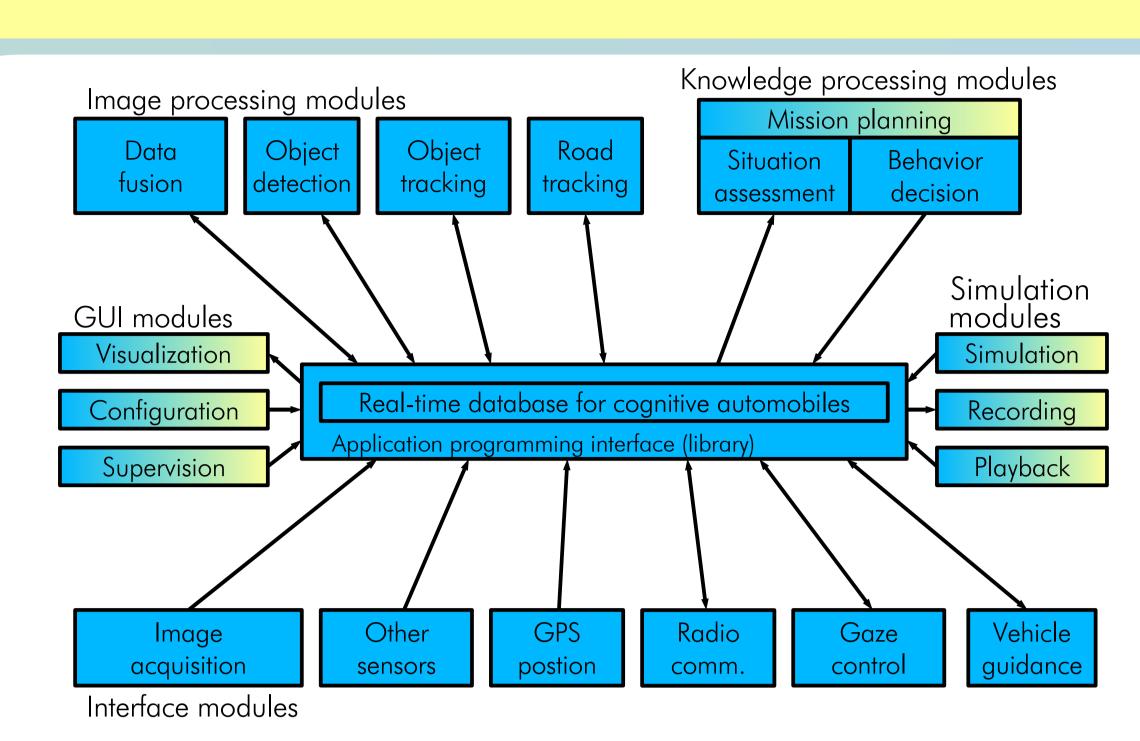

#### Functional Architecture

- Architectural requirements of cognitive automobiles:

- Distinct levels of information processing with specific temporal resolutions and real-time requirements

- Extensive information needs by all software modules for subsequent data fusion and verification

- Combination of algorithms with different approaches

- Functional overview:

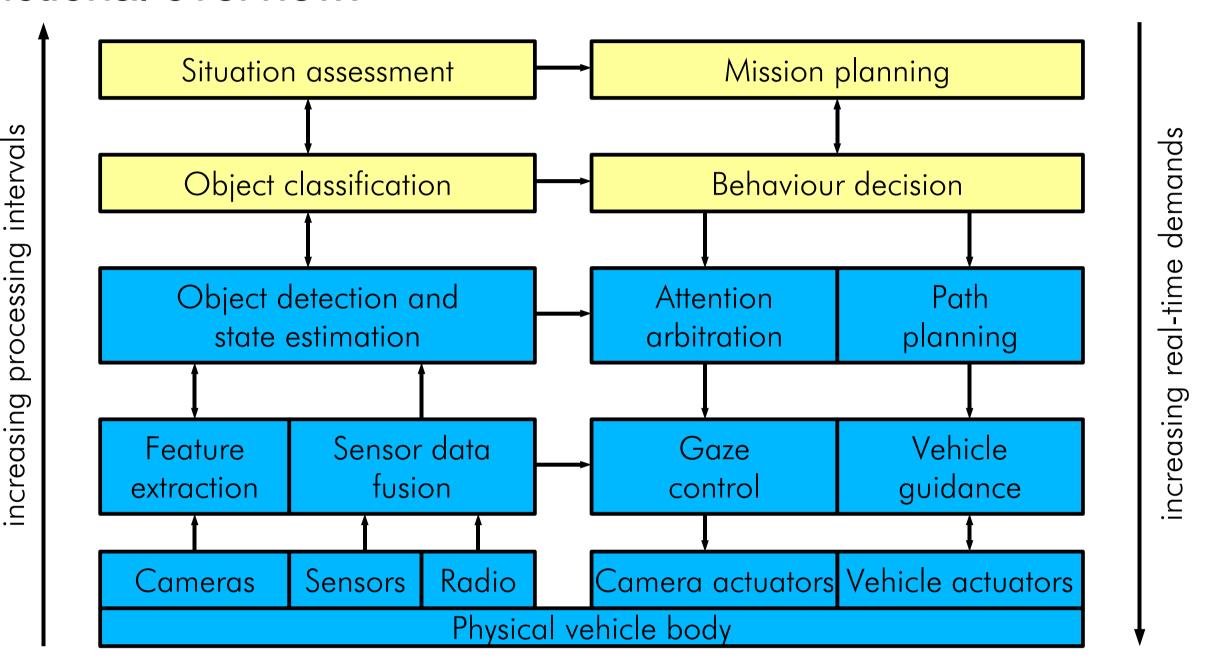

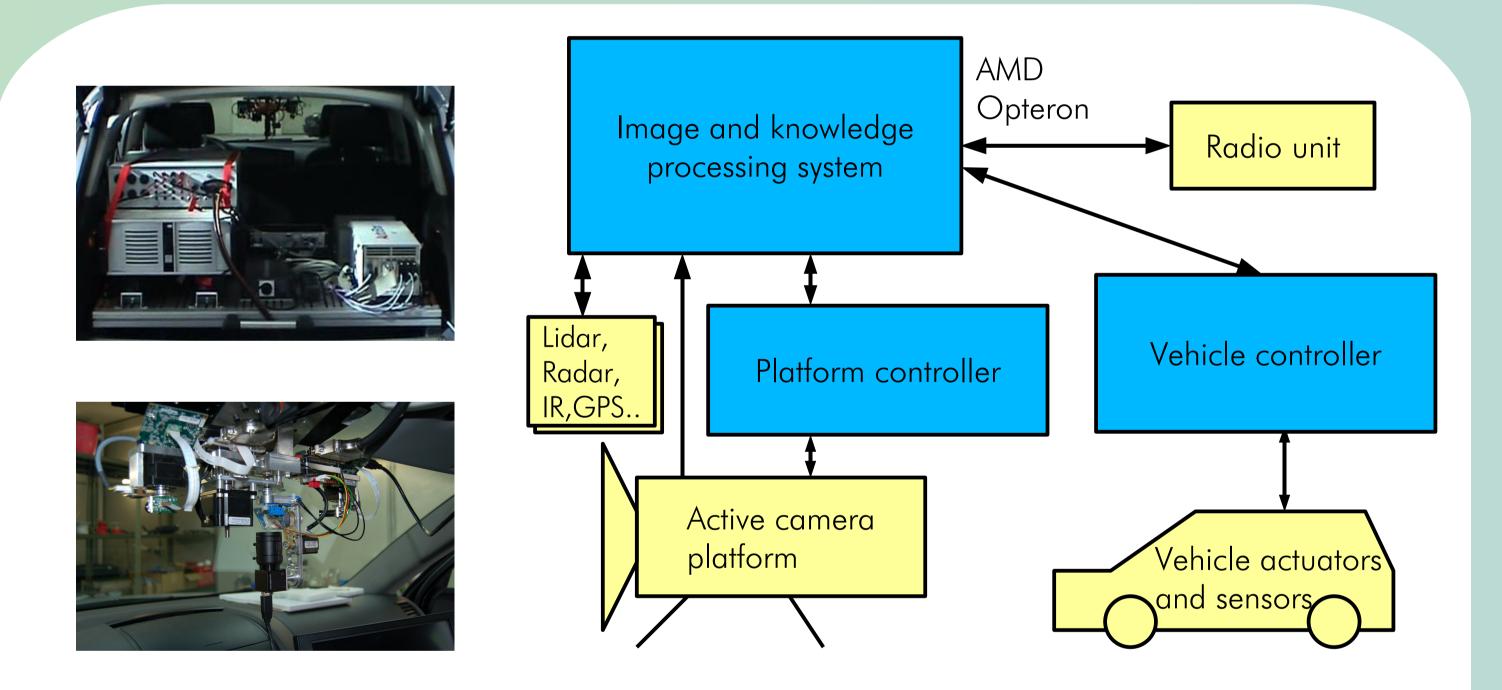

#### Hardware Architecture

- Selected multicore multiprocessor system provides:

- Fast computation for image processing

- I/O bandwidth for image and sensor data acquisition

- Large memory for knowledge processing

- Parallel execution of cognitive functions

- Low latencies for interprocess communication

- Powerful storage for logging (RAID, Flash)

- AMD Opteron regarded as "Cluster-in-a-box":

CAN WLAN LAN VGA HD

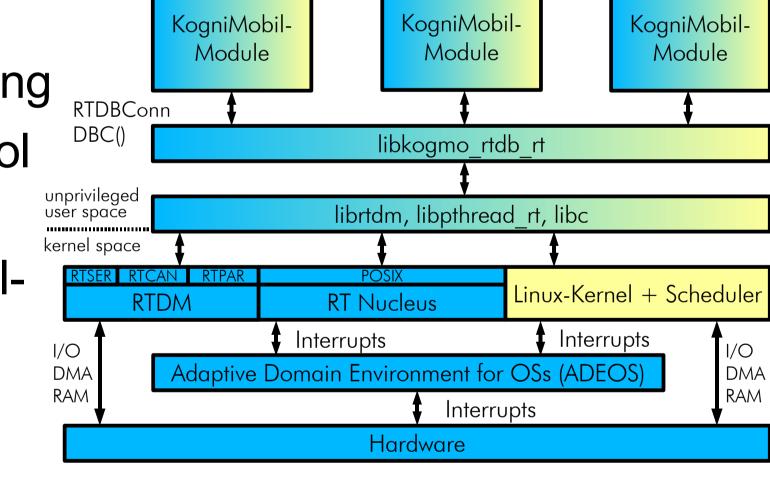

### Software Architecture

- Real-time database "KogMo-RTDB" as integration framework:

- Central publication of relevant information (raw sensor data, tracked objects, situation and generated behavior)

- Open access for maximum transparency between all cognitive layers

- Unified interface also for simulation and situation replay

- Intuitive API that provides methods to

- publish and update own data objects

- search and retrieve objects from other modules

- wait for updated data and new objects by others (trigger)

- Temporal decoupling with history buffers and consequent use of timestamps for submitting and querying objects

- Coherent view at the situation for slower modules

- Seamless integration of real-time and non real-time modules :

- Hard real-time for critical control processes

No interference from visualisation and logging

Lock-less write protocol prevents blocking

- Dynamic switch to realtime mode to prevent priority inversion

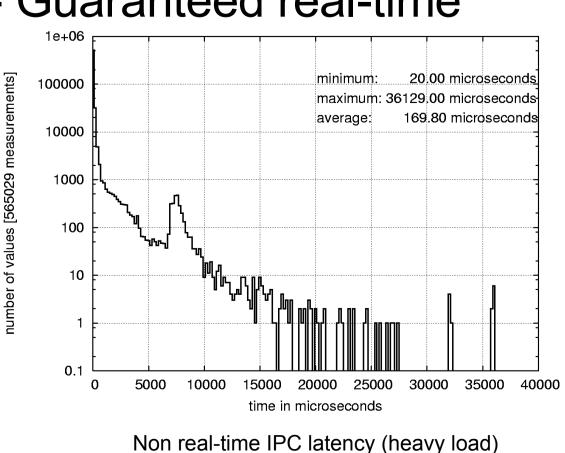

## Experimental Results

- Comprehensive architecture used in several vehicles

- Powerful integration platform for tight cooperation of all cognitive modules

- Measurement results of key operations show:

- Low overhead

- Fast response

- Guaranteed real-time

Time (average, min-max, in  $\mu$ s) **Operation** (heavy load) non real-time <u>real-time</u> 122.5, 39- 93109 75.6, 38-273 Insert Delete 18.5, 4- 41250 18.5, 8-131 22.6, 5-181681 | 25.6, 6-134 WriteData ReadData 17.0, 4- 10721 16.8, 4-62 IPC-Latency 169.8, 20- 36129 | 66.5, 21-208

100000 microseconds maximum: 208.00 microseconds average: 66.48 microseconds average: 66.48 microseconds time in microseconds

Real-time IPC latency (heavy load)